# Optimisation of dV/dt – Losses Trade Off using Switchable Gate Resistance

System-level effects in power converters are often caused or constrained by behaviour of the power semiconductor devices, for example high dV/dt from modern IGBTs. Bulky and lossy dV/dt filters are often required in high-power converters to limit the voltage stress on insulation of wound components, e.g. motors. By taking advantage of real-time bi-directional communication over the fibre-optic link, Amantys gate drives reduce the need for dV/dt filtering through intelligent selection of gate resistance, thus enhancing the overall system performance and power density.

By Dr Angus Bryant, Amantys Power Electronics Limited

#### Introduction

The rate of change of voltage, dV/dt, generated by the power semiconductors in an inverter bridge has a significant impact on any wound components connected to its output. In a motor drive, the interaction of cable impedance and motor winding capacitance causes overvoltages in the windings depending on the dV/dt generated in the inverter. Limiting the dV/dt is often a key requirement in power converter and motor drive design, which results in bulky and lossy dV/dt filters at the converter output or excessive demands on wound component insulation.

In order to mitigate this effect on converter design, the source of the excessive dV/dt – the power semiconductors, typically IGBTs and diodes – should be controlled to reduce the dV/dt generated. However, this increases the switching losses significantly, reducing the converter current rating because of thermal limitations.

This article explores a unique feature of Amantys gate drives, which have selectable (switchable) gate resistances. These may be used dynamically during converter operation to optimise the trade-off between dV/dt and switching loss. This results in a significant improvement in losses for a given dV/dt, making possible for the first a realistic alternative to passive dV/dt filters to reduce the stress on machine windings.

# Switchable Gate Resistances on Amantys Gate Drives

Amantys gate drives feature Power Insight, which is a two way communications protocol between the converter controller and the gate drive. Data is superimposed on top of the PWM switching command and feedback / acknowledge signal. This allows online configurability of the gate drive; for example, the converter designer can modify gate resistor vales (Rg\_on, Rg\_off and Rg\_soft\_off) and gate-emitter capacitances (Cge)

without removing the gate drives from the inverter stack or interrupting device switching. This opens the door to selection of gate resistances appropriate to different converter operating conditions while the converter is switching.

# **Switching Test Results**

To assess the opportunity presented by selecting gate resistances during operation, a candidate IGBT module was subjected to double pulse switching tests. An industry-standard IGBT, rated at 4500 V/1200 A in a 190 x 140 mm package, was switched at room temperature. Switching energy losses and voltage rise/fall times were recorded, with the latter used to calculate dV/dt. The tests were repeated at different off-state voltages and on-state currents, and with different gate resistances.

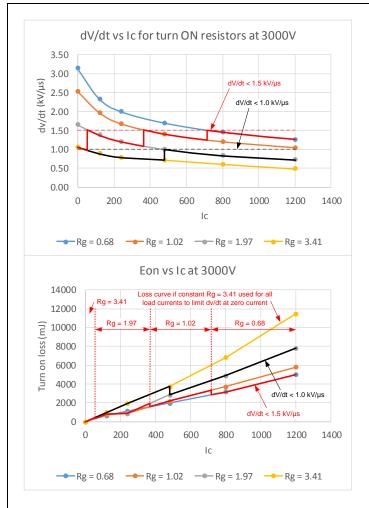

Figure 1 shows the effect of on-state current on dV/dt for different turn-on gate resistances (Rg\_on). As expected, the dV/dt decreases at higher currents; the zero-current dV/dt is at least double that at rated current. The corresponding turn-on energy losses are also shown, with a near-linear relationship between loss (E on) and on-state current. With a larger gate resistance, the trend is for reduced dV/dt but increased IGBT switching loss; the effect on the diode is to reduce both its reverse recovery loss and its switching stress (peak power dissipation, the limit of which is defined in the reverse recovery safe operating area). Corresponding data was also gathered for the dV/dt at IGBT turn-off, although the dV/dt is largely current-independent. However, given that the turn-on switching loss is typically greater than or equal to the turn-off energy loss, the potential to make substantial improvements lies with improving the tradeoff at IGBT turn-on.

Figure 1 – dV/dt (upper) and turn-on energy loss (lower) dependence on on-state current. Red curves: dV/dt constrained to 1.5 kV/µs; black curves: 1.0 kV/µs.

Gate resistance Rg\_on is given in ohms.

Closer examination of Figure 1 reveals the advantages to be gained from selecting Rg\_on based on the current. Using the example dV/dt constraint of 1.5 kV/µs (as shown by the red curve) below an on-state current of about 70 A the largest gate resistance (3.41  $\Omega$ ) is used. While this restricts the dV/dt to less than 1.5 kV/µs, it results in very little extra turn-on loss because of the small load current. Above this current, the gate resistance would reduce to 1.97  $\Omega$ , resulting in a lowerloss trajectory for E\_on vs current. Similar changes in Rg occur at about 350 A and 720 A, with the effect that Rg\_on is selected to give the lowest energy loss while maintaining a dV/dt less than or equal to the constraint. A similar pattern is shown with a constraint of 1.0 kV/µs (black curve), albeit with larger Rg on required to achieve this. Clearly, as the constraint increases in value, the smaller the resistance can be at a given current, thus minimising the impact on turn-on energy loss of a constrained dV/dt.

# Resistance Selection Strategy

The strategy used to select the gate resistance value Rg\_on is therefore set in the converter controller:

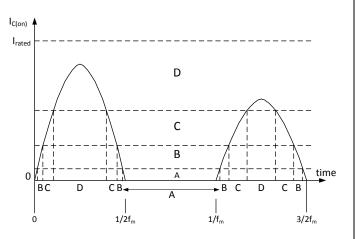

Figure 2 – Examples of how Rg\_on is selected using the on-state current.

- 1. Current measured in the controller.

- Rg\_on value selected based on the current.

- 3. Rg\_on value sent to the gate drive ready for the next turn-on event.

- 4. Controller commands the gate drive to turn on.

- 5. Process repeats for next switching cycle.

Figure 2 shows an example pattern of Rg\_on selection for two amplitudes of AC current in a phase leg. The Rg\_on value selected (A to D) depends on the *instantaneous* current measured by the controller.

#### Effect on Losses

While the curves in Figure 1 show the effect of the technique on switching losses, the effect on converter losses is more important to assess the system impact. Simple average loss calculations, following a similar method to the equations in [1,2], were carried out for the following conditions:

DC link voltage: 3000 V

• AC output current: 849 A rms

AC output voltage: 1653 V rms line-line

Power factor: ±0.866 pu (30°/150° lagging, i.e. inverting/rectifying respectively)

• Switching frequency: 400 Hz

On-state curves were taken from the manufacturers' datasheets, with switching losses taken from the dV/dt-constrained measured data (as shown in Figure 1).

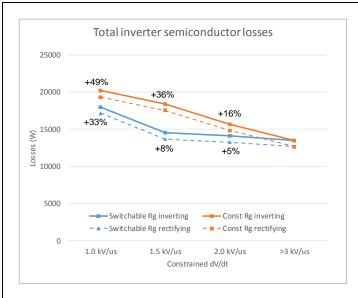

The resulting inverter stack losses (3 phases, i.e. 6 IGBTs and 6 diodes) are shown alongside constrained dV/dt in Figure 3. Four cases are shown: switchable Rg and constant Rg, each for inverting (pf = +0.866 pu) and rectifying (pf = -0.866 pu) operation.

In the constant Rg case, the resistance value is chosen for *all currents* to limit the worst-case dV/dt at zero current. Clearly this is a poor strategy; the loss increase is significant as the dV/dt is constrained to smaller values, with almost 50% loss increase at 1.0 kV/µs.

Figure 3 – Trade-off curves of inverter stack losses vs constrained dV/dt. The ">3 kV/µs" case is unconstrained (i.e. the base case). The percentages are loss increases relative to the base case.

By using switchable Rg, the impact on inverter losses is reduced, especially at 1.5 kV/µs and above. For example, restricting the dV/dt to 1.5 kV/µs may allow a significant improvement in machine efficiency (or reduction in dV/dt filter losses, cost or size) for a modest 8% increase in inverter losses. Using constant Rg to restrict the dV/dt would in contrast increase losses by 36% which is clearly undesirable.

# Integration into a Converter

The mechanism to select Rg\_on and Rg\_off is to use Power Insight communications over the fibre optic link to the gate drive. This avoids an extra fibre channel being used to select the resistance, or the need for the gate drive to sense the current.

In most Amantys Gate Drives, there are 63 values for each of Rg\_on and Rg\_off to choose from. In practice, there are extra values between the four shown in Figure 1, so the converter designer may decide to change resistance value at more points in between, giving smoother profiles of dV/dt and losses against current.

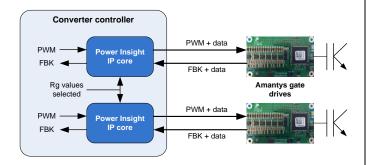

While Power Insight functionality is already built into Amantys Gate Drives, the converter controller would need such functionality adding to send the resistance commands to the gate drives. The functionality required can be licensed from Amantys as an IP block for integration into the customers' controller, as shown in Figure 4.

Figure 4 – Integration of Amantys Power Insight into a converter controller (e.g. FPGA handling PWM generation and I/O) using an IP block.

## Further Switching Trade-Off Improvements

It is not only the trade-off of dV/dt against switching losses that can be improved by dynamic selection of gate resistance. At high DC link voltages, the voltage overshoot at IGBT turn-off must be limited, which is only feasible for continuous operation by increasing Rg\_off. (The extent to which this is feasible is IGBT-dependent.) This is not usually possible using constant Rg, because of the large increases in switching losses (and resulting restriction of current rating) for nominal DC link voltages.

However, increasing Rg\_off *only* when the DC link voltage exceeds a certain threshold is a feature available on most Amantys Gate Drives and this does not require communication with the converter controller. It is useful in applications where an increase in voltage must be tolerated for short periods (or at low current) without affecting nominal rating, e.g.:

- Solar inverters at low loads

- DC-fed rail traction inverters

- Wind converters (high voltage ride-through)

## **Conclusions**

This article has explored the application of selectable (switchable) gate resistances to optimise the trade-off between dV/dt and switching loss, using real-time bi-directional communication over the fibre-optic link. The need for dV/dt filtering is reduced, thus enhancing the overall system performance and power density, and reducing stress on the electrical machine.

### References

- [1] K. Berringer, J. Marvin and P. Perruchoud, "Semiconductor Power Losses in AC Inverters," in IAS Conf. Rec., p. 882, Orlando, Oct 1995.

- [2] A. Wintrich, U. Nicolai, W. Tursky and T. Reimann, "Application Manual Power Semiconductors," SEMIKRON International GmbH, 2015.

Email: info@amantys.co.uk